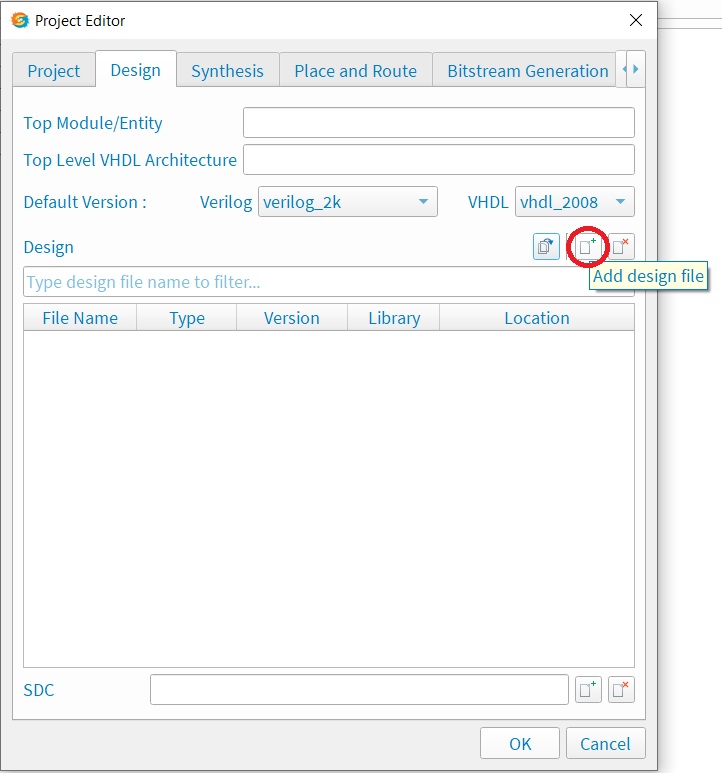

Efinity IDE from Efinix - Getting Started Tutorial - Logic - Electronic Component and Engineering Solution Forum - TechForum │ Digi-Key

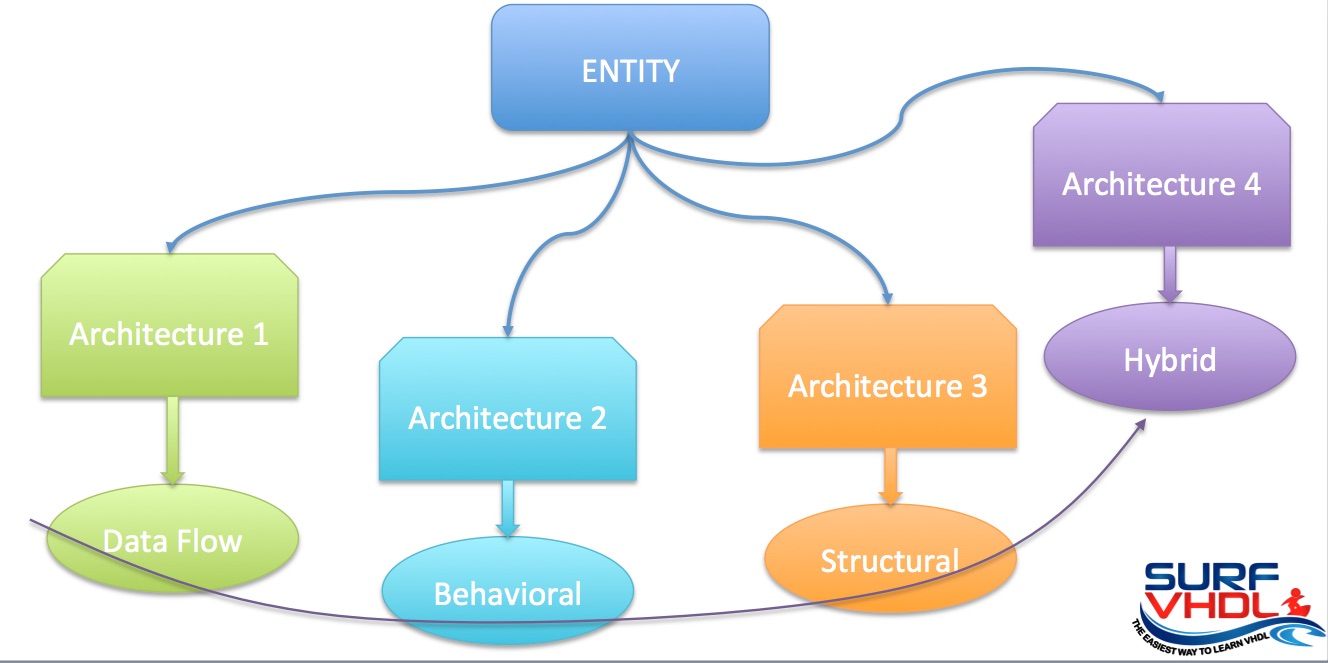

Laboratory 6 Experiment on Hierarchical VHDL Design | ETEC 373 | Lab Reports Digital Systems Design | Docsity